## Dependable design of modern LSI

|                             | (20) (E)            |                                                                                    |        |                            |  |  |

|-----------------------------|---------------------|------------------------------------------------------------------------------------|--------|----------------------------|--|--|

| Name                        | KATO Kentaro        |                                                                                    | E-mail | k-katoh@tsuruoka-nct.ac.jp |  |  |

| Status                      | Associate Professor |                                                                                    |        |                            |  |  |

| Affiliations                |                     | IEICE, IEEE                                                                        |        |                            |  |  |

| Keywords                    |                     | LSI, Reliability                                                                   |        |                            |  |  |

| Technical<br>Support Skills |                     | <ul><li>LSI CAD</li><li>Circuit design with I</li><li>Design of embedded</li></ul> |        |                            |  |  |

## Research Contents Dependable design of modern LSI

As scaling of semiconductor technology increases, the performance of technology increases. However, modern LSI fabricated with less than 20nm technology is suffered from serious reliability problems.

This research is about dependable design of modern LSI.

The target devices are as follows.

- -Micro processor

- -System on a chip

- -FPGA

Etc.

This research deals with the following reliability techniques.

- -On chip delay measurement technique

- -Small delay defect detection

- -Soft error detection and correction

- -Yield learning

Etc.

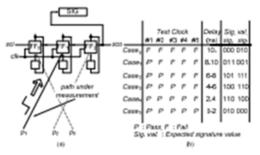

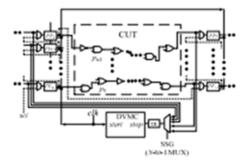

Figures 1 and 2 show some of techniques we proposed.

Fig. 1 On-chip path delay measurement using signature register. Fig. 2 On-chip path delay measurement using TDC.

## Available Facilities and Equipment

| Digital Oscilloscope, MSOX3034A (Agilent Technologies) |  |

|--------------------------------------------------------|--|

|                                                        |  |

|                                                        |  |

|                                                        |  |

|                                                        |  |